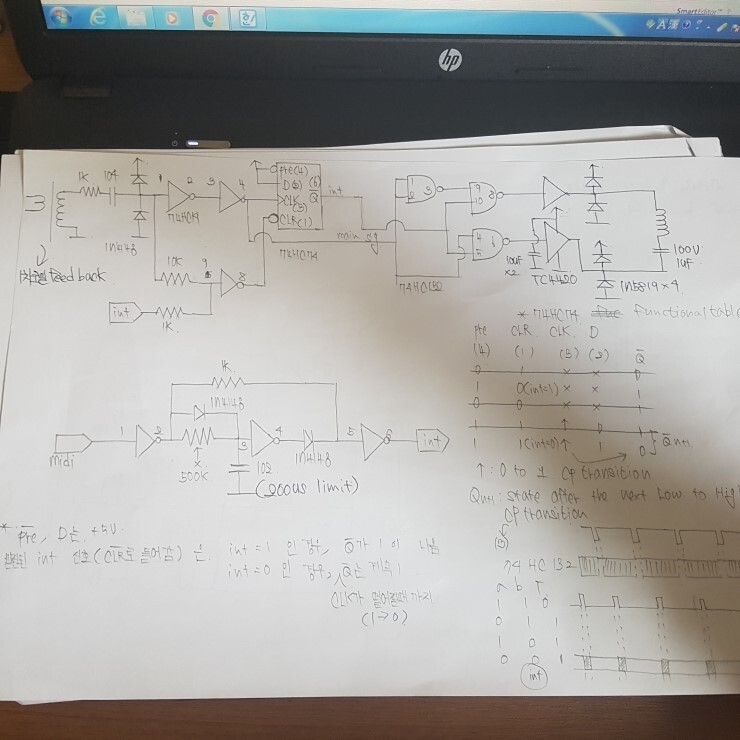

이번에 제작할 계획인 DRSSTC1을 위한 하프브릿지 구동회로입니다.(로직과 드라이버칩의 전원을 빠드렸습니다)

ENABLE 구성의 모스펫 드라이버 칩의 수급이 쉽지 않음으로 현재 가지고 있는 74HC132와 TC4420으로 대체했습니다.

SSTC의 경우 D플립플롭 구성을 제거해도 되지만 DRSSTC의 경우 인터럽트 신호가 0이 되는 시점과 피드백 신호가 0이 되는 시점이 어긋나게 되면 전력부 스위칭소자는 D-S간 많은 전류가 흐르는 상태에서 turn-off를 시켜야하는 상황이 생기며 이런 경우는 소자에게 굉장한 스트레스를 주게 됩니다. 많은 양의 물이 흐르는 벨브를 잠그는것이 텅 비어있는 벨브를 잠그는것보다 어려운것과 유사한 맥락입니다.

이런 상황을 방지하기 위해 플립플롭을 도입하게 됩니다. 이런 구성은 인터럽트 신호가 OFF되도 플립플롭의 클럭에 들어가는 메인 발진신호가 0이 될때까지 플립플롭의 반전출력에서 나오는 '모종의 처리가 이뤄진 인터럽트 신호'는 계속 ON되어있습니다. 이렇게 함으로서 정확한 ZCS을 구현할 수 있습니다. DRSSTC의 경우 1차코일에도 공진회로가 들어가 과도상태에서 동작하게 되는데 이런 상황에서 소자의 하드스위칭을 막기위한 노력의 일환이라 보면 될것같습니다.

PWM제한회로의 경우 ontime을 200us으로 제한을 두었습니다.

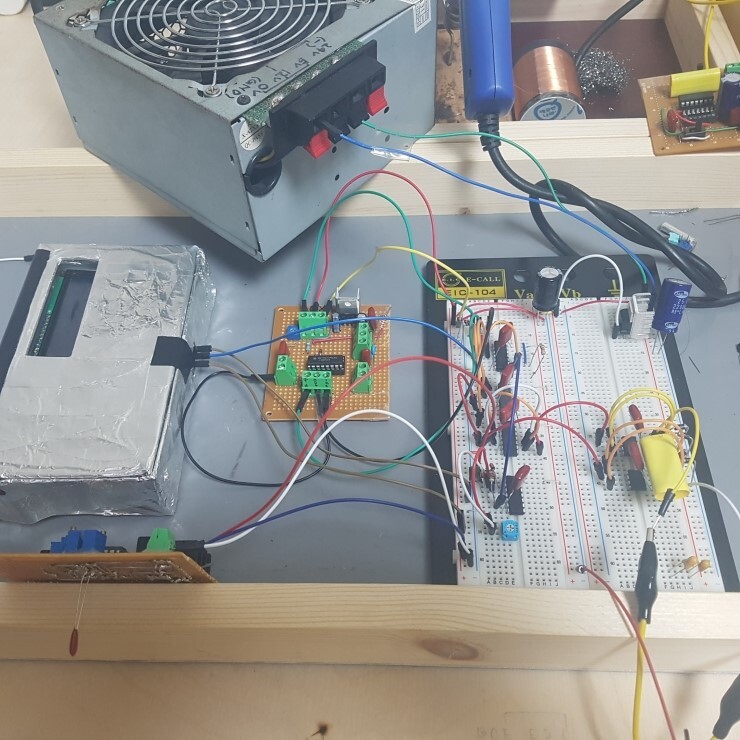

회로테스트.

케리어신호의 경우, 일전에 만든 다용도발진회로를 통해 500khz로 구형파를 생성하여 피드백신호 대용으로 입력해주었습니다.

인터럽트신호의 경우 인터럽터 박스의 신호를 넣어줄수도 있으나, 듀티사이클을 좀 올려보기위해 TL494 모듈의 1KHZ구형파를 이용했습니다. 듀티사이클은 0~50%까지 가변할 수 있습니다.

지금까지 만들어본것에 비해 상당히 많은 로직이 들어가는데, 리니어한 구성이라 생각보다 간단합니다.

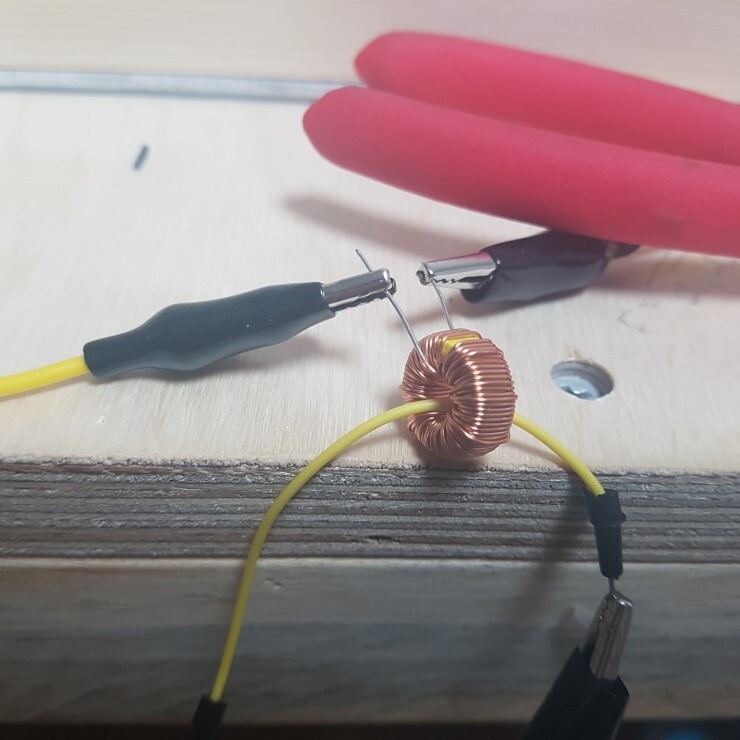

실험용 게이트 드라이버 트랜스포머(GDT)의 경우 위와 같은 구성을 차용했습니다.

GDT에 사용할만한 전선이 없는데 걱정이네요..

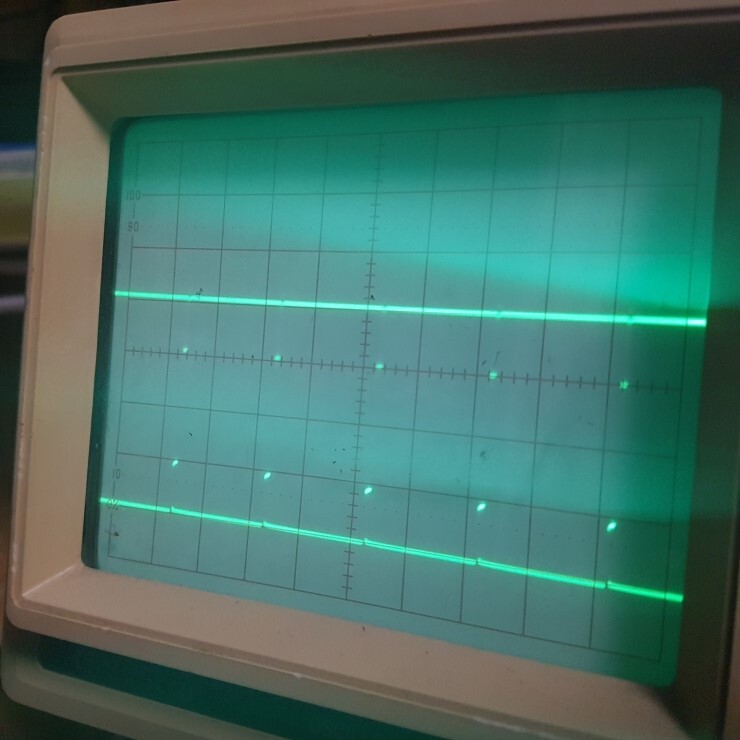

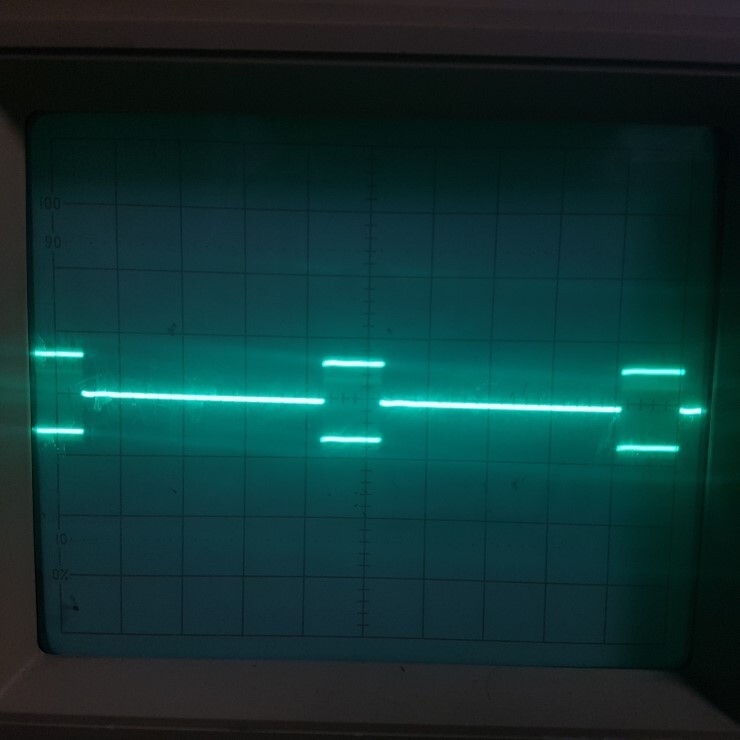

아래가 인터럽트 신호이고 위가 74HC132의 출력파형입니다.

제가 좀 햇갈린 부분이 이곳인데요, ENABLE기능이 있는 모스펫 드라이버를 쓰게 되면 아래 파형과 모스펫드라이버칩의 파형이 동일하지만 이러한 드라이버칩을 대체하기위해 74HC132를 쓰게 되면 반전된 파형을 얻게됩니다.

만일 인터럽트 신호의 듀티사이클이 3%이면 74HC132 출력의 듀티는 97%처럼 보이게 됩니다.

문제가 있을까 싶어 이웃분께 문의해본결과 3%의 듀티사이클이나 97%나 GDT를 통과하게 되면 같게 취급할수 있으므로 상관없다고 합니다.

DRSSTC의 경우 GDT가 들어가 위와 같이 이용할 수 있으나 다른 용도로 적용할 경우 74HC132의 출력을 반전시켜야 ENABLE 기능이 있는 드라이버칩과 완전히 동일한 기능을 하게 됩니다.

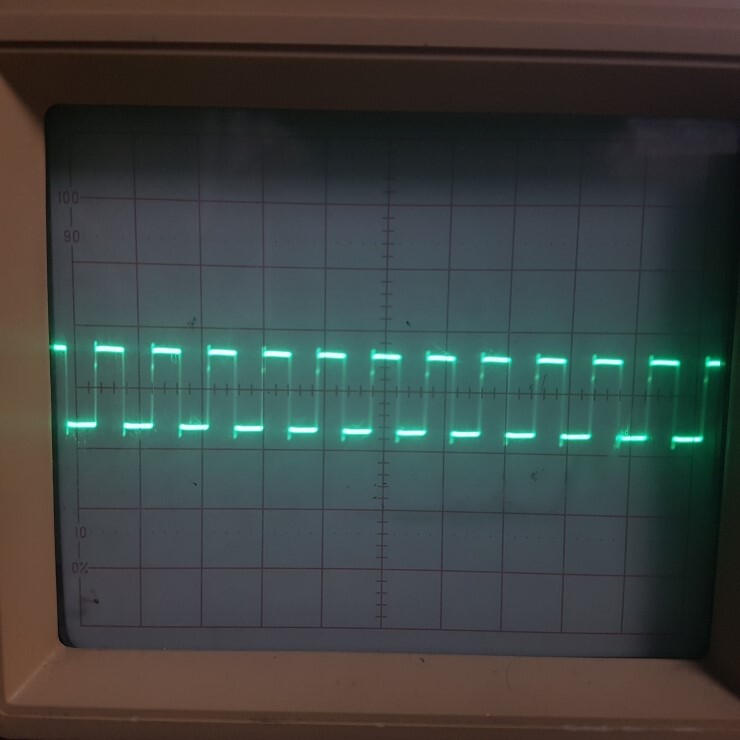

GDT를 통과한 최종파형. 원하는대로 잘 나오네요..

저 네모난 부분을 확대해보면 아래와 같은 파형이 나옵니다.

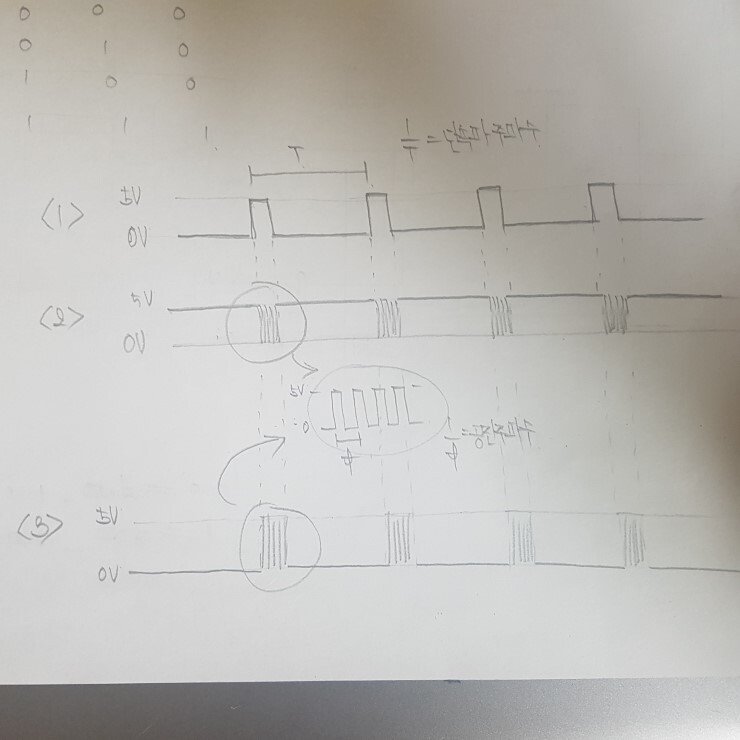

이해를 돕기위한 모식도..

발진신호가 500KHZ이고 이 신호를 단속시키지 않고 동작시키면 CW모드라 불립니다. 원리상 가청주파수를 넘기에 소리가 들리지 않는다 생각할 수 있으나 사실 코로나노이즈 등이 껴 시끄러운 소리가 나게 됩니다.

위의 500KHZ신호를 1초에 100번, 즉 100HZ로 단속시키면(위 사진에서 네모부분이 1초간격에 100번 들어간다는 말입니다) 스트리머에서 100HZ의 소리가 나게 되며 이런 원리로 뮤지컬테슬라코일을 만들 수 있습니다.

이러한 변조기법을 pulse density modulation(PDM) 혹은 pulse repetition modulation(PRM)이라고 합니다.

이제 만능기판에 옮긴후 전력부를 설계해야겠습니다.

'Project > DRSSTC' 카테고리의 다른 글

| 기준 주파수 발생기 제작 (0) | 2022.02.10 |

|---|---|

| DRSSTC1-드라이빙회로 기판제작과 만능기판 레이아웃 (0) | 2022.02.10 |

| DRSSTC 1- 미디 인터럽터(MIDI interrupter) 박스 제작 (0) | 2022.02.08 |

| DRSSTC1-듀티 사이클 제한회로 (duty cycle limiter) (0) | 2022.02.08 |

| DRSSTC프로젝트 시작 (0) | 2022.02.08 |